Serial FPDP sensor data link scales up to 20 gigabytes per second

By Andrew Reddig

High-performance embedded computing systems continue to have an insatiable need for raw sensor data. With continuing improvements in general-purpose processors as well as the increasing use of field-programmable gate arrays (FPGAs) for advanced signal processing, computers are able to process more data than ever before. However, getting data from the sensor to the processor continues to be a challenge. General-purpose interfaces, such as Gigabit and 10 Gigabit Ethernet have interoperability advantages, but typically are too complex for sensor endpoints. Proprietary interfaces create difficulties in development, verification, and test due to the lack of a standards-based ecosystem. The Serial FPDP standard, ANSI/VITA 17.1-2003, has provided a middle ground solution that works in many applications, but needs to be updated to meet the throughput requirements of today’s sensors and processors.

Today’s Serial FPDP

The ANSI/VITA 17.1-2003, or serial Front Panel Data Port (FPDP), standard provides a relatively simple protocol for point-to-point data links between a sensor and a processor, using more than 99 percent of the available throughput with a minimum of protocol overhead. In addition to link efficiency, the simplicity of the protocol makes it easy to implement a Serial FPDP endpoint in an FPGA or even complex programmable logic device (CPLD) without needing a general-purpose processor. By keeping the sensor end of the link as simple as possible, Serial FPDP allows many applications to use an open standard but still fit within the severe space, weight, and power limitations typically found for imaging focal plane arrays, RF antennas, or other external sensors.

The Serial FPDP standard supports three data rates: 1.0625 GBd, 2.125 GBd, and 2.500 GBd. Control and data packets are encoded using 8B/10B encoding, resulting in data transfers at 247 megabytes per second using a 2.5 GBd serial link after encoding and protocol overhead. Serial FPDP links support a wide range of physical interfaces with the most common option being 2.5 gigabits per second multimode fiber. Serial FPDP interfaces are available as off-the-shelf I/O modules from several manufacturers in a range of form factors, including PCI and PCI Express cards for workstations as well as IEEE 1386.1 PMC and VITA 42 XMC modules for embedded applications. In addition to off-the-shelf modules, Serial FPDP IP cores are also available for FPGAs, making it easy for a sensor developer to embed Serial FPDP into a sensor with little risk. If necessary, Serial FPDP analyzers are also available for test, validation, and debug of Serial FPDP interfaces.

The next generation

When Serial FPDP was originally developed, it was designed to replace the parallel ANSI/VITA 17-1998 FPDP standard which was limited to 160 megabytes per second of throughput. Because of the limitations of sensor and processor technology at the time, this speed was more than adequate for most applications. However, the capabilities of both sensors and processors have grown since then, with today’s high-performance sensors providing several channels of data at gigabytes per second for each channel. At the same time, fiber-optic interface technology has also improved, with individual links up to 5 and even 10 gigabits per second becoming more common. In addition to link speed, fiber-optic transceiver packaging density is also increasing, with off-the-shelf options for 4, 8, and even 12 fibers in one high-density package using a multi-fiber ribbon connector.

To meet the needs of faster sensors and processors, a version of Serial FPDP is being developed. Designated VITA 17.2 and in final draft, the standard adds three major enhancements to Serial FPDP. First, the standard includes a wider range of link speeds, supporting individual fiber data rates up to 6.25 GBd. Second, the concept of “channel bonding” is introduced, allowing up to 32 physical fiber-optic links to be combined into one logical Serial FPDP stream. Finally, the standard adds some protocol enhancements to improve synchronization and link reliability.

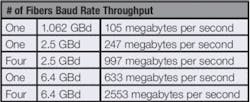

By combining a faster serial link rate with channel bonding, Serial FPDP supports streams from 105 megabytes per second (1-by-1.0625 GBd) up to 19.7 gigabytes per second (32-by-6.25 GBd), with a wide range of options in between. As a result, sensors such as a 2 gigasamples-per-second, 10-bit A-D converter can implement one logical Serial FPDP stream at 20 gigabits per second, transport it across four fibers at 6.4 GBd, and present the data to a processing system using an off-the-shelf VITA 17.2 I/O module as one recombined stream. With the previous version of Serial FPDP, the sensor would have needed to multiplex the data across four fibers in a proprietary format and then recombine the data at the other end. By using VITA 17.2 channel bonding, the multiplexing and demultiplexing is performed by the Serial FPDP core, using an open standard to make the interface easier to implement and debug.

Product example

Serial FPDP endpoints are typically implemented in FPGA devices, whether as part of a custom sensor circuit board or within an off-the-shelf I/O module. The flexibility of an FPGA-based architecture makes it straightforward to support legacy Serial FPDP as well as the 17.2 standard with one hardware design.

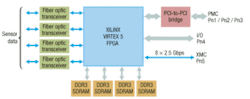

A typical FPGA-based Serial FPDP product is Tekmicro’s JazzFiber-V5 PMC / XMC I/O module. This product, shown in the block diagram below, uses a Xilinx Virtex 5 FPGA as the Serial FPDP engine. The Xilinx V5 LXT device supports serial bit rates up to 3.75 gigabits per second, meeting the legacy Serial FPDP data rates, while the FXT device goes up to 6.4 gigabits per second to meet the entire range of 17.2 speeds. In the legacy Serial FPDP mode, each fiber-optic interface is used for a separate Serial FPDP link, resulting in throughputs up to 1 gigabytes per second (4-by-247 megabytes per second). When using 17.2 mode with channel bonding, the four are combined into one logical stream at up to 2.5 gigabytes per second when using the maximum Serial FPDP rate of 6.4 GBd. The range of throughput options is shown in the table below.

The use of Virtex 5 FPGA technology also supports the use of higher speed DDR3 memory, providing the buffer memory throughput necessary to support the higher sensor data rates. Each memory bank supports 16-bit memory clocked at 400 MHz, double-data-rate, for aggregate memory bandwidth of 6.4 gigabytes per second. This allows the maximum Serial FPDP throughput of 2.5 gigabytes per second to be buffered using DDR3 memory as a deep FIFO, decoupling the I/O module from processor latencies.

Andrew Reddig is chief executive officer and chief technology officer of TEK Microsystems Inc. in Chelmsford, Mass. His e-mail address is [email protected].