By John Rhea

Field programmable gate arrays, or FPGAs, are muscling their way into electronic systems where by application specific integrated circuits, or ASICs, once dominated. This trend is well established among commercial users and is spreading to the embedded commercial off-the-shelf (COTS) areas of high-reliability applications.

In parallel with this trend, the lines of demarcation are blurring between general-purpose microprocessors and the more specialized digital signal processors (DSPs) traditionally optimized for computationally intensive tasks. Last year's introduction of the Motorola Altivec chip, as the fourth generation of its dominant PowerPC family, has further accelerated that trend.

The net result is a growing number of choices for design in meeting the diverse criteria of complex programs, as measured in economic considerations, product lead times, production runs, and reliability. Even in the relatively low-volume military and aerospace applications, there are sufficient technology alternatives to enable users to make the best decisions.

"FPGAs are changing the landscape of the COTS-embedded DSP market by extending the reach of these open-architecture, board-level products into application areas that previously required custom board designs," maintains Rodger Hosking, vice president of DSP board designer Pentek Inc. in Upper Saddle River. N.J.

At Pentek, engineers are applying FPGA technology to a new generation of software radios, because they say FPGAs are outperforming DSPs, Hosking says.

Over the past 20 years programmable logic devices of all types — for standard COTS as well as for custom designs — remained almost exclusively within the scope of hardware, he explains. Designers saw them as a convenient and flexible replacement for gates, control logic, memory, and other traditional devices.

Accordingly, once engineers completed the hardware design, they did not change the programmable logic "firmware" unless they had to incorporate new hardware features. Also, if a software engineer discovered a problem that he couldn't solve by changing his DSP program, he would have to prevail upon the hardware engineer to change the underlying logic design, Hosking explains.

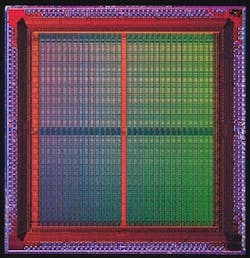

But over the past five years FPGAs have made dramatic gains in several critical areas to accommodate DSP functions, he notes. The gate density of the most advanced FPGAs has tracked the famous law of Intel Corp. co-founder Gordon Moore, doubling about every year and a half, and is now up to 10 million gates per device.

Moreover, chip designers typically structure gate arrays as logic cells equipped with memory and are capable of performing math functions. These high-density logic cells are available in a wide range of basic "cores" to support fast multipliers, block memory to handle fast Fourier transform (FFT) processing, and distributed memory for various filters.

Further adding to the appeal of FPGAs are the high-level cores that third party vendors offer to complement standard cores from FPGA vendors. These range from complete DSPs to applications-specific blocks like high-speed Internet modems. "With these new off-the-shelf functions," Hosking concludes, "FPGAs are now able to penetrate both the general-purpose ASIC market as well as the DSP market."

Officials at Actel Corp. in Sunnyvale, Calif., a major supplier of FPGAs, make a case for their advantage over ASICs in terms of lower non-recurring engineering (NRE) costs, quicker turnaround for urgent military requirements, and greater suitability for the low volumes inherent in military and other high reliability applications.

"An ASIC vendor wants to see at least half a million parts," says Bob Pecotich, high reliability product line manager at Actel. Yet, he adds, a typical 500-aircraft program will need only 4,000 to 10,000 parts, including spares. Furthermore, Pecotich points out, wafer fabrication facilities, or fabs, are running at full capacity. This includes the captive fabs and foundries.

ASICs will do the job in more stable environments involving high volumes and long lead times spanning the design through the procurement phases, he says, but that does not always square with the military's unique requirements. Pecotich cites the case of the buildup to the Persian Gulf conflict in 1991, when U.S. forces found they needed upgrades to their satellite imaging systems and infrared night vision devices. These had to be "designed in the fox hole," he says, and "FPGAs got it nailed."

The high volume requirement for ASICs is based in part on amortizing the NRE. "ASICs always require NRE," notes Ken O'Neill, product marketing director at Actel, but for FPGAs "we absorb the NRE ... our FPGAs are a standard product."

How much NRE? Pecotich calculates that a relatively standard ASIC for a high-volume application to be supplied by a fabless vendor will require at least $700,000 up front. O'Neill estimates that the NRE in the military market runs two to three times more than for commercial users.

There is another advantage of FPGAs over ASICs, O'Neill says, and it is the inherent security of parts using the company's antifuse technique. Once they have been programmed, he says, they are impossible to reverse engineer.

As a sort of refresher course for users, Actel supplies a definition of antifuse: a programmable element consisting of a two-terminal device that exhibits high impedance in the unprogrammed state and low impedance in the programmed state. One programs the device by applying a high voltage across the antifuse's terminal, causing a dielectric breakdown.

The underlying trend is a converging of functions, he Actel officials agree. While DSPs are optimized for repetitive functions microprocessors are very adaptable. Still, both these functions are becoming embedded in FPGAs.

What makes this possible is the greater functionality on a chip, as the semiconductor industry moves down the submicron scale of feature size. The advantage here, notes Pecotich, is eliminating the timing delays in chip-to-chip connections.

For example, phased array radars in the 1960s and 1970s used relatively simple controls to operate the entire array. Yet the new technology gives each radar element its own controller. Chip packaging can be plastic or ceramic, including ball grid arrays.

Application-specific modules

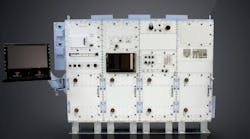

In parallel with this trend, experts at the U.S. Defense Advanced Research Projects Agency (DARPA) in Arlington, Va., have been working for more than five years on a further integration into what they call application-specific electronic modules, or ASEMs. These are similar to multi-chip modules (MCMs) widely used in the industry today, and put complex functions on a substrate. Since these are often hybrid functions, they cannot always go on the same substrate. When optimized for the application, however, they can tolerate the timing delays.

Peter Milliken is ASIC product line manager at Aeroflex UTMC in Colorado Springs, Colo., a company that specializes in the radiation-hardened market for space applications. Milliken contends that ASICs have a place in this market niche. This spring Aeroflex UTMC introduced a line of gate arrays called the Strategic RadHard line, commercially fabricated with the complementary metal oxide silicon (CMOS) process at a feature size of 0.6 micron and capable of withstanding 1 megarad of total-dose radiation.

For parts like these, Milliken maintains, "I can be cheaper than the FPGAs." The company's strategy is to use commercial FPGAs to do product development and then phase over with a NRE investment for the ASIC. "We work out the bugs with the FPGA," he says, and get a quick payback with a volume of 10,000 to 100,000 parts. He estimates the NRE at $75,000 for a top-of-the-line part with an average selling price of $2,000.

While military volumes are less than those for equivalent commercial parts, life cycles are not, he notes. These longer cycles require longer commitments to maintain supplies, and Aeroflex UTMC does continuing in-house development. This cuts the lead time for limited runs from three to six months to market to two to three months.

Milliken also points out that the technology can migrate with the decreased feature sizes (and accompanying increased wafer size) to stave off obsolescence. The company's new product line uses 0.6-micron resolution, which translates into 100 millimeter or five-inch wafers, which he calls compact discs. Next step is to 0.25 micron on 200 millimeter or eight-inch "pancake" wafers and eventually to 0.13 micron on 300 millimeter (twelve-inch) wafers comparable to 78 rpm long-playing records — for those whose memory goes back that far.

Moreover, the company's new line of gate arrays is not limited to space and other high reliability applications. Aeroflex UTMC is guaranteeing single event upset (SEU) immunity with this line, and Milliken says that this can also be valuable in commercial avionics applications involving high-altitude aircraft.

At Sky Computers Inc., a board vendor in Chelmsford, Mass., Stephen Paavola, product line marketing manager, says his engineers try to avoid ASICS where possible, but adds, "FPGAs don't solve all problems." While FPGAs are pervasive in personal computers and similar applications, company designers have been looking at custom silicon for fast serial databuses, including low-voltage devices.

Sky experts have considered custom chips for their SkyChannel interconnect, Paavola says, but have not had to do so yet. They have built custom chips for crossbar connections, but this was a relatively simple design.

"We like FPGAs," Paavola says. "They give us custom flexibility with off-the-shelf technology ... FPGA costs are down and performance is up." He adds that Sky tries to avoid custom ASICs except in low volume situations and when the devices provide a verifiable performance advantage.

Xilinx Inc. in San Jose, Calif., is a major provider of FPGAs to the hi-rel market. Rick Padovani, director of aerospace and defense products, says he has done his own tradeoff studies to determine the real cost of ownership when compared with ASICs.

For openers, he points out, enhancements and debugging take place in real time using actual silicon rather than in a simulation environment, as with an ASIC flow. This eliminates what he calls the agonizing wait for prototypes to be returned from the fab.

Real estate issues

But flexibility has a price as well, according to Padovani. FPGA architectures carry what he describes as "gate overhead" to gain programmability. This means that FPGAs generally have larger silicon areas for the same functions than their standard cell counterparts.

Here is where new semiconductor technology makes the difference. At 0.25-micron feature sizes and smaller, available gates virtually become a non-issue, according to Xilinx studies. Random access memory, or RAM, and other enabling features, such as improved input/output (I/O) can replace these gates.

Remote upgradeability is another plus for FPGAs. "Any system that can be remotely accessed can also be remotely upgraded," according to Padovani. This is important in competitive commercial markets since each change or upgrade to a fixed logic device such as an ASIC requires a full re-design, plus the accompanying product development. This becomes particularly troublesome for today's deep sub-micron devices.

This is also an issue for military users, and Padovani cites work Xilinx did for Raytheon TI Systems in McKinney, Texas, on a forward looking infrared (FLIR) system used across several military platforms.

FPGAs topped ASICs in Raytheon's tradeoff studies because of greater confidence that FPGA providers would continue their commitment to the hi-rel market, but the payoff was in field upgradeability. This could be done cost-effectively by reconfiguring the firmware of the programmable read only memory, or PROM, according to the Raytheon studies.

Altera Corp., San Jose, Calif. introduced a further refinement, in June at the Embedded Processor Forum, also in San Jose. This is a new system on a programmable chip (SOPC) designated Excalibur, which is aimed at meeting the stringent time-to-market requirements while reducing the design risks and costs inherent in ASICs and embedded processors.

"We believe the trend away from a fixed system on a chip [SOC] methodology toward a highly flexible SOPC solution will accelerate dramatically," Altera chief executive officer Rodney Smith told the conference.

In conjunction with the Excalibur announcement, Altera also introduced an embedded processor designated Nios that provides a general purpose reduced instruction set computer (RISC)-based processor core optimized for programmable logic. The resulting Excalibur device thus combines the embedded processor with memory and logic to provide the programmable flexibility of programmable logic devices (PLDs) with the computing power of microprocessor, once again blurring the lines between traditional devices.

Another approach is at QuickLogic Corp. in Sunnyvale, Calif., where designers are combining embedded functions from application-specific standard products (ASSPs) and a high-speed FPGA to create what the company calls an embedded standard product, or ESP.

The idea is to capitalize on the benefits of FPGAs, such as flexibility, short development cycles, and low development cost without paying the price later in higher device costs and lower performance, says Jon Ewald, military marketing program manager at QuickLogic. ASSPs guarantee functionality with high performance and low cost, but suffer from a fixed instruction set and are not easily adaptable, according to the company.

By integrating standard products, QuickLogic officials say they hope to circumvent the issues of licensing and NRE, and to enable the company to eat away at the FPGA market with its ESPs. Moreover, Ewald asserts his company's commitment to the military and aerospace market. "While many semiconductor suppliers have abandoned the market, "QuickLogic's military program is expanding to provide a complete solution for the military OEM [original equipment manufacturer]," he says.

CPU Tech's Comfort sees new opportunities for system on a chip

The new generations of programmable logic devices are expanding vistas for design engineers among high-end, complex programs. Still, another set of opportunities exist for the idea of a system on a chip (SOC), says Richard Comfort, vice president at CPU Tech in Pleasanton, Calif. This set of opportunities concern old systems that designers can modernize without additional software costs, and implement technologically feasible but cost-prohibitive applications.

On one point there is general agreement, Comfort says: SOC is the next generation beyond the microprocessor. By integrating microprocessors and support chips into a single part, SOCs reduce power requirements, size, and weight to where designers can use them where microprocessor-based systems are not practical.

However, these advantages have been limited to high-volume consumer applications due to high development and verification costs, Comfort says. The challenge is to migrate this technology to the low-volume, high-reliability systems — and do it cost-effectively.

The payoff is worth the effort, Comfort maintains. "Valuable software for avionics and weapons systems can be preserved intact," he says. "Obsolescence issues are solved ... permanently."

The CPU Tech strategy is to insert scaleable SOC technology into existing designs. Comfort cites the work the company has already done since it was selected in August 1998 to provide SOCs equivalent to the old MIL-STD 1750A airborne computer.

As a subcontractor to Honeywell Defense Avionics Systems, in Albuquerque, N.M., CPU Tech has been providing the SOC for the display generator in the U.S. Air Force's F-16 fighter. Now, CPU Tech engineers are working on a $100 million program to apply SOC technology to a modernization kit for a radar processing system on the F-16s.

"Today, high-end embedded systems contain numerous microprocessors and hundreds if not thousands of components to support them," Comfort says. "SOC can integrate the microprocessors and support chips into a single part. The benefits in the form of miniaturization and portability are clear.

"But SOC also makes it possible to modernize existing systems, dramatically improving reliability and maintainability and reducing manufacturing costs," he adds. "This means that the life cycles of many useful, functioning devices can be extended and new markets for them can be developed."

Comfort focuses on two near-term possibilities for effective use of SOC technology: general aviation and medicine.

In the case of general aviation, the collision avoidance systems built for commercial airliners were costly to develop and are too expensive and too large for general aviation. His solution is to scale such a system by inserting a compatible SOC module that would not only improve it, but reduce the price and size to where the owners of small private planes could install it, thus dramatically increasing the market for the product and improving the safety of air travel.

Regarding medical testing and monitoring devices, Comfort notes that these were once found only in major hospitals because of their cost and maintenance requirements. His solution here is portable machines that patients can operate from home. Connected by Internet to central databases and monitored by duty personnel, these SOC products could provide new levels of safety and convenience for patients. To be practical, however, they must incorporate existing software and provide high levels of reliability.

CPU Tech's CEO and founder, Ed King, sums up the situation this way: "Our ability to compatibly scale high-reliability systems represents the lowest risk path to the next generation of computing technology beyond the microprocessor." — J.R.