Bus simulator tool to generate bit-error-rate contours for JEDEC spec introduced by Keysight

The test & measurement software product, which is available as an add-on to Advanced Design System (ADS) 2014.11 from Keysight, calculates DQ and DQS eye probability density distributions and BER contours for memory interfaces.

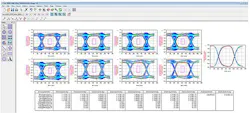

The simulator achieves this through use of statistical simulation. It constructs the eye diagram from the transmitter, channel and receiver impulse responses, and from the stochastic properties of a conceptually infinite non-repeating bit pattern.

The ADS DDR Bus Simulator offers DQ and DQS eye calculations to arbitrarily low BER levels, including the 1E-16 contour specified by JEDEC. The simulator accounts for crosstalk and asymmetry between rising and falling switch times, and provides timing and voltage margins between the contour and DDR4 receive mask specification.

The ADS DDR Bus Simulator allows for three IC model types: built-in, IBIS or circuit models; all of which can be "mixed and matched" in a schematic. The built-in driver and receiver contain de-emphasis and continuous-time linear equalization capabilities, respectively.

For more information contact Keysight online at www.keysight.com.

Related content

Fast logic analysis system for high-end digital test and measurement introduced by Keysight

Agilent spins off electronic test and measurement businesses into new company named Keysight Technologies

Debug tool to help DDR memory designers with precompliance testing introduced by Agilent.