Raytheon eyes advanced heterogeneous computing architectures packaged in system-on-chip (SoC)

Officials of the U.S. Air Force Research Laboratory at Wright-Patterson Air Force Base, Ohio, announced a $4.6 million contract on Wednesday to the Raytheon Space and Airborne Systems segment in El Segundo, Calif., for the Run-Time Configurable Accelerator (RCA), Domain-specific System on Chip (DSSoC) Program.

The Air Force awarded the contract on behalf of the U.S. Defense Advanced Research Projects Agency (DARPA) in Arlington, Va., which runs the DSSoC project as part of the DARPA Electronics Resurgence Initiative (ERI).

The RCA DSSoC program seeks to capitalize on machine learning, advanced heterogeneous processor capability, general-purpose processors, and on ARM computing software and hardware capabilities to develop new tools, and hardware technologies.

Related: Heterogeneous computing combines benefits of CPUs, GPUs, and FPGAs

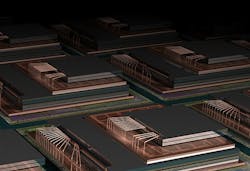

The DSSoC program seeks to develop a heterogeneous system-on-chip (SoC) composed of many cores that mix general-purpose processors, special-purpose processors, hardware accelerators, solid-state memory, and input/output (I/O).

The project seeks to enable rapid development of multi-application systems through a single programmable device.

This effort involves building runtime-reconfigurable hardware and software that enable near application-specific integrated circuit (ASIC) performance without sacrificing programmability for data-intensive algorithms.

Related: The future of high-performance embedded computing

Raytheon experts will try to create a hardware and software system that enables data-intensive algorithms to run at near ASIC efficiency without the cost, development time, or single-application limitations typically found in ASIC development.

The DARPA Electronics Resurgence Initiative seeks to ensure far-reaching improvements in electronics performance well beyond the limits of traditional scaling. It focuses on architectures; design; and materials and integration for the next wave of U.S. semiconductor advancement.

For more information contact Raytheon Space and Airborne Systems online at www.raytheon.com, the Air Force Research Laboratory at www.wpafb.af.mil/afrl, or DARPA at www.darpa.mil.

Ready to make a purchase? Search the Military & Aerospace Electronics Buyer's Guide for companies, new products, press releases, and videos