Varioscale to develop advanced imaging for process verification of tiny integrated circuits

Officials of the U.S. Air Force Research Laboratory at Wright-Patterson Air Force Base, Ohio, announced a $23.8 million contract to Varioscale earlier this month for the Rapid Analysis of Various Emerging Nanoelectronics (RAVEN) project.

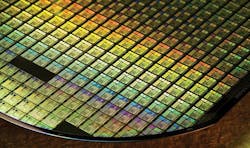

RAVEN focuses on developing an analysis tool capable of imaging minimum size circuit features on a silicon integrated circuit chip for process verification and failure analysis. The Air Force Research Lab awarded the contract on behalf of the U.S. Intelligence Advanced Research Projects Activity (IARPA) in Washington.

The RAVEN program encompasses four major areas for the tool development: rapid acquisition of images from a bare die; real-time image analysis with in-situ feedback to minimize or eliminate reworks due to image anomalies; innovative algorithms for reconstructing the images of individual device layers and the overall device; and computational resources for acquiring, moving, storing, and analyzing petabyte size data files.

Related: ON Semiconductor capacitive touch control IC simplifies design of touch sensor applications

The project involves destructive and non-destructive image acquisition techniques. IARPA is the research arm of the U.S. Office of the Director of National Intelligence.

Between 2011 and 2015, the semiconductor industry saw significant advances in both the scaling of integrated circuits and 3-D integration of several wafers, monolithically grown stacked circuits, and non-CMOS structures, IARPA officials explain.

Microprocessors of 14-nanometer size have been in production since July 2014 and 7-nanometer circuits were demonstrated at Albany Nanotech in early 2015. Samsung Corp., Taiwan Semiconductor Manufacturing Co. (TSMC), and GlobalFoundries have announced plans to ship production-quality 10-nanometer integrated circuits in late 2016.

Intel plans to ship 10-nanometer integrated circuits in 2017, and TSMC plans to offer 7-nanometer chips in 2017. Manufacturing at these technology nodes will require high-speed and high-resolution image acquisition for process verification and failure analysis.

The RAVEN program involves imaging metal, polysilicon, vias, contacts, shallow trench isolation (STI) regions, and dielectrics. The project may involve X-ray based microscopes, high brightness scanning electron systems, multi-beam scanning electron microscopes, non-scanned projected image electron systems, ion beam imaging systems, ultra-high resolution interference optical microscopes, and several array AFM systems.

IARPA officials say they expect several companies to be involved in the RAVEN program, so the contract to Varioscale most likely will not be the only one.

The five-year RAVEN program has three phases. The two-year first phase will develop a laboratory bench-top or demonstration test tool. The two-year second phase will develop an alpha prototype tool and application demonstration, and the one-year third phase will refine the initial prototype into a beta tool suitable for use in a research environment.

For more information contact Varioscale online at www.varioscale.com, the Air Force Research Lab at www.wpafb.af.mil/afrl, or IARPA at www.iarpa.gov.

Learn more: search the Aerospace & Defense Buyer's Guide for companies, new products, press releases, and videos