Air Force and NASA to define next-generation radhard space microprocessor for the spacecraft of 2020-2030

KIRTLAND AIR FORCE BASE, N.M., 5 March 2013. U.S. Air Force and NASA radiation-hardened microprocessor experts are kicking off a program to define a next-generation space computer for rad-hard applications based on anticipated space processor needs from 2020 to 2030.

The Air Force Research Laboratory (AFRL) released a presolicitation Friday (BAA-RVKV-2013-02) for the Next Generation Space Processor (NGSP) Analysis program, which seeks to perform a 3 month evaluation of anticipated space computer applications for 2020 to 2030; and distill a set of goals for a future space microprocessor architecture.

Sponsoring the NGSP Analysis are scientists at the AFRL Space Vehicles Directorate (AFRL/RV), and the NASA Space Technology Mission Directorate-Game Changing Development program (NASA/STMD-GCD).

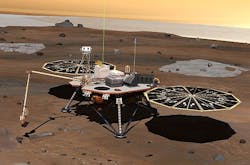

Ultimately, the Air Force and NASA want to define a space-qualifiable rad-hard multicore processor architecture for manned and unmanned spacecraft.

The NGSP Analysis program also will produce a simulation model of the proposed processor architecture that will predict the processor's power use to provide realistic performance estimates.

Benchmark applications will include autonomous pinpoint landing with hazard detection and avoidance during entry, descent and landing of missions to the moon and Mars; real time segmented mirror control for large space based telescopes; onboard real-time analysis of multi-megapixel level hyperspectral image data; autonomous onboard situational analysis and real time mission planning; and real time model based spacecraft level fault protection.

A follow-on program, potentially worth as much as $20 million, would be to develop a space microprocessor for high-performance space computing for advanced space missions through 2030. The microprocessor will be based on commercially available microprocessor technology modified for space applications, Air Force researchers say.

Experts say they want the Next Generation Space Processor to execute several concurrent applications and parallel processing across the set of cores; have at least 24 processor cores that support 32-bit words have at least one terabyte of memory, and support floating-point processing.

The next-generation space processor also must perform 24 billion operations per second and 10 billion floating point operations per second and consume no more than 7 Watts of power, with the ability to turn off unused cores and other resources.

The processor also must have a sleep mode in which it consumes no more than 100 milliwatts of power, and prevent errors by enforcing partitioning of groups of cores, interconnects and memories into fault containment regions.

The processor also must have a non-volatile memory boot ROM port able to boot the processor, have four to eight DDR3/4 memory ports, support DMA transfers between external I/O ports and external memory, have eight 10-gigabit-per-second serial I/O ports, industry-standard interfaces, a generic serial interface that connects to an external protocol converter such as an field-programmable gate array (FPGA) or custom device, and a serial interface to an FPGA or other kind of reconfigurable co-processor.

The NGSP also must have a dedicated test and debug interface; operate cascaded or tiled devices; have symmetric and asymmetric hypervisor software; run the Linux operating system; and have a C an C++ application software compiler.

More details about the NGSP Analysis program will be released later this month.

For questions or concerns contact the Air Force's Gabriel Mounce by phone at 505-846-6079 or by email at [email protected] or Lt. Holly Bradley by phone at 505-846-0841 or by email at [email protected].

Also contact NASA's Tibor Balint by phone at 202-358-2368 or by email at [email protected], or Raphael Some by phone at 818-354-1902 or by email at [email protected].

More information is online at https://www.fbo.gov/spg/USAF/AFMC/AFRLPLSVD/BAA-RVKV-2013-02/listing.htm.

About the Author

John Keller

Editor-in-Chief

John Keller is the Editor-in-Chief, Military & Aerospace Electronics Magazine--provides extensive coverage and analysis of enabling electronics and optoelectronic technologies in military, space and commercial aviation applications. John has been a member of the Military & Aerospace Electronics staff since 1989 and chief editor since 1995.