Software-development for design and development tools worst-case execution time analysis introduced by LDRA

WIRRAL, England – LDRA in Wirral, England, is introducing an upgraded LDRA software-developmenttools that supports the hardware-based multicore mitigation capabilities of RISC-V processors such as Microchip, Synopsys, and ANDES Technology.

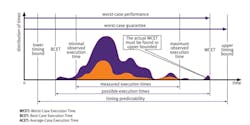

Developers can access and optimize RISC-V-based multicore systems, including analyzing shared resources and data coherency on worst-case execution time.

Continuous development

These design and development tools enable developers to automate worst-case execution time analysis as part of continuous development. This worst-case execution time inclusion streamlines design, increases reliability, accelerates time-to-market, and guarantees deterministic execution in software-intensive aerospace, defense, avionics, automotive, industrial, energy, and medical applications.

The LDRA tool suite supports multicore RISC-V architectures that address multicore contention in hardware. This support gives developers access to the full suite of LDRA tools, including static and structural coverage analysis, MISRA compliance and extensive reporting capabilities, all while taking full advantage of RISC-V-based multicore mitigation capabilities.

For more information contact LDRA online at https://ldra.com.